# MALLA REDDY COLLEGE OF ENGINEERING & TECHNOLOGY

(Autonomous Institution – UGC, Govt. of India) Sponsored by CMR Educational Society

(Affiliated to JNTU, Hyderabad, Approved by AICTE - Accredited by NBA & NAAC - 'A' Grade - ISO 9001:2008 Certified)

Maisammaguda, Dhulapally (Post Via Hakimpet), Secunderabad – 500100, Telangana State, India.

Contact Number: 040-23792146/64634237, E-Mail ID: <a href="mailto:mrcet2004@gmail.com">mrcet2004@gmail.com</a>, website: <a href="www.mrcet.ac.in">www.mrcet.ac.in</a>

# MASTER OF TECHNOLOGY VLSI & EMBEDDED SYSTEMS

# DEPARTMENT OF ELECTRONICS AND COMMUNICATION ENGINEERING

COURSE COVERAGE SUMMARY AND QUESTION BANK ACADEMIC YEAR: 2016-2017

# DEPARTMENT OF ELECTRONICS & COMMUNICATION ENGINEERING M.TECH – VLSI & EMBEDDED SYSTEMS COURSE STRUCTURE

# I YEAR I SEMESTER

| S.NO. | SUBJECT<br>CODE                  | SUBJECT                                                                                                                              | L | T/P/D | C   |     | AX<br>RKS |

|-------|----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|---|-------|-----|-----|-----------|

|       |                                  |                                                                                                                                      |   |       |     | INT | EXT       |

| 1     | R15D6801                         | VLSI Technology & Design                                                                                                             | 4 | -     | 3   | 25  | 75        |

| 2     | R15D6802                         | CPLD & FPGA Architectures & Applications                                                                                             | 4 | -     | 3   | 25  | 75        |

| 3     | R15D6803                         | Embedded System design                                                                                                               | 4 | -     | 3   | 25  | 75        |

| 4     | R15D6804<br>R15D6805<br>R15D6806 | ELECTIVE-I  1.Digital System Design  2.CMOS Analog Integrated Circuit Design  3.Hardware Software Co-design                          | 4 | •     | 3   | 25  | 75        |

| 5     | R15D6807<br>R15D6808<br>R15D6809 | ELECTIVE-II  1.CMOS Digital Integrated Circuit design  2.Algorithms for VLSI Design Automation  3.Advanced Digital Signal Processing | 4 | -     | 3   | 25  | 75        |

| 6     | R15D5802<br>R15D5803<br>R15D5812 | OPEN ELECTIVE –I  1.Advanced Operating Systems  2.Computer System Design  3.Web Services and Service oriented Architecture           | 4 | -     | 3   | 25  | 75        |

| 7     | R15D6881                         | VLSI Laboratory                                                                                                                      | - | 3     | 2   | 25  | 75        |

| 8     | R15D6882                         | Technical Seminar-I                                                                                                                  | - | -     | 2   | 50  | -         |

|       |                                  | 24                                                                                                                                   | 3 | 22    | 225 | 525 |           |

## I YEAR II SEMESTER

| S.NO. | SUBJECT<br>CODE | SUBJECT L T/P/D C                           |    | C |    | IAX<br>ARKS |     |

|-------|-----------------|---------------------------------------------|----|---|----|-------------|-----|

|       |                 |                                             |    |   |    | INT         | EXT |

| 1     | R15D6810        | <b>Embedded Real Time Operating Systems</b> | 4  | - | 3  | 25          | 75  |

| 2     | R15D6811        | CMOS Mixed Signal Circuit Design            | 4  | - | 3  | 25          | 75  |

| 3     | R15D6812        | Low Power VLSI Design                       | 4  | - | 3  | 25          | 75  |

|       | R15D6813        | ELECTIVE – III  1.Adhoc –Wireless Networks  |    |   |    |             |     |

| 4     | R15D6814        | 2.Digital Signal Processors & Architectures | 4  | - | 3  | 25          | 75  |

|       | R15D6815        | 3.Embedded Networking                       |    |   |    |             |     |

|       | R15D6816        | ELECTIVE- IV  1.System On Chip Architecture |    |   |    |             |     |

| 5     | R15D6817        | 2.Design For Testability                    | 4  | - | 3  | 25          | 75  |

|       | R15D6818        | 3.Multimedia Signal Coding                  |    |   |    |             |     |

|       |                 | OPEN ELECTIVE- II                           |    |   |    |             |     |

|       | R15D5805        | 1.Natural Language Processing               |    |   |    |             |     |

| 6     | R15D5810        | 2.Advanced Network Programming              | 4  | - | 3  | 25          | 75  |

|       | R15D5816        | 3.Grid and Cloud Computing                  |    |   |    |             |     |

| 7     | R15D6883        | Embedded Systems Laboratory                 | -  | 3 | 2  | 25          | 75  |

| 8     | R15D6884        | R15D6884 Technical Seminar-II               |    | - | 2  | 50          | -   |

|       |                 | Total                                       | 24 | 3 | 22 | 225         | 525 |

# II YEAR I SEMESTER

| S.NO. | SUBJECT<br>CODE | SUBJECT                        | L | T/P/D | C  | MAX<br>MARKS |     |

|-------|-----------------|--------------------------------|---|-------|----|--------------|-----|

|       |                 |                                |   |       |    | INT          | EXT |

| 1     | -               | <b>Project Review Seminars</b> | - | -     | 4  | -            | -   |

| 2     | -               | Project Work                   | 1 | -     | 18 | -            | -   |

|       | Total           |                                |   | -     | 22 |              | •   |

## II YEAR II SEMESTER

| S.NO. | SUBJECT<br>CODE | SUBJECT           | L | T/P/D | C  | MAX<br>MARKS |     |

|-------|-----------------|-------------------|---|-------|----|--------------|-----|

|       |                 |                   |   |       |    | INT          | EXT |

| 1     | -               | Project Work      | 1 | 1     | 22 | ı            | -   |

| 2     | -               | Project Viva-voce | 1 | 1     | ı  | ı            | -   |

| Total |                 | -                 | - | 22    | •  | -            |     |

# **I-SEMESTER**

# **CONTENTS**

| S.NO | SUBJECT                                      | PG.NO |

|------|----------------------------------------------|-------|

|      | I-SEMESTER                                   |       |

| 1    | VLSI TECHNOLOGY AND DESIGN                   | 7     |

| 2    | CPLD AND FPGA ARCHITECURES AND APPLICATIONS  | 15    |

| 3    | MICROCONTROLLERS FOR EMBEDDED SYSTEMS DESIGN | 22    |

| 4    | DIGITAL SYSTEM DESIGN                        | 28    |

| 5    | CMOS ANALOG INTEGRATED CIRCUIT DESIGN        | 36    |

| 6    | CMOS DIGITAL INTEGRATED CIRCUIT DESIGN       | 43    |

|      | II-SEMESTER                                  |       |

| 1    | EMBEDDED REAL TIME OPERATING SYSTEMS         | 47    |

| 2    | CMOS MIXED SIGNAL CIRCUIT DESIGN             | 54    |

| 3    | LOW POWER VLSI DESIGN                        | 60    |

| 4    | DIGITAL SIGNAL PROCESSORS AND ARCHITECTURES  | 68    |

| 5    | SYSTEM ON CHIP ARCHITECTURE                  | 78    |

| 6    | GRID AND CLOUD COMPUTING                     | 81    |

#### VLSI TECHNOLOGY AND DESIGN

#### UNIT -I: Review of Microelectronics and Introduction to MOS Technologies:

MOS, CMOS, BiCMOS Technology. Basic Electrical Properties of MOS, CMOS & BiCMOS Circuits:  $I_{ds}$  –  $V_{ds}$  relationships, Threshold Voltage V T , G m , G ds and  $\omega$  o , Pass ransistor, MOS, CMOS & Bi CMOS Inverters,  $Z_{pu}$  / $Z_{pd}$ , MOS Transistor circuit model, Latch-up in CMOS circuits.

#### **UNIT -II: Layout Design and Tools:**

Transistor structures, Wires and Vias, Scalable Design rules, Layout Design tools.

#### **Logic Gates & Layouts:**

Static Complementary Gates, Switch Logic, Alternative Gate circuits, Low power gates, Resistive and Inductive interconnect delays.

#### **UNIT –III: Combinational Logic Networks:**

Layouts, Simulation, Network delay, Interconnect design, Power optimization, Switch logic networks, Gate and Network testing.

#### **UNIT –IV: Sequential Systems:**

Memory cells and Arrays, Clocking disciplines, Design, Power optimization, Design validation and testing.

#### **UNIT -V: Floor Planning:**

Floor planning methods, Global Interconnect, Floor Plan Design, Off-chip connections.

#### **TEXT BOOKS:**

- 1. Essentials of VLSI Circuits and Systems, K. Eshraghian Eshraghian. D, A. Pucknell, 2005, PHI.

- 2. Modern VLSI Design Wayne Wolf, 3 rd Ed., 1997, Pearson Education.

#### **REFERENCE BOOKS:**

- 1. Introduction to VLSI Systems: A Logic, Circuit and System Perspective Ming-BO Lin, CRC Press, 2011.

- 2. Principals of CMOS VLSI Design N.H.E Weste, K. Eshraghian, 2 nd Ed., Addison Wesley.

# VLSI TECHNOLOGY AND DESIGN

# COURSE COVERAGE SUMMARY

| S.No | TEXT BOOK<br>TITLE                          | Chapters in<br>Text Book | Units / Topics Covered                                                   | AUTHOR                       | PUBLISHERS | EDITION                      |

|------|---------------------------------------------|--------------------------|--------------------------------------------------------------------------|------------------------------|------------|------------------------------|

| 1    | Essentials of VLSI<br>Circuits &<br>Systems | 1,2                      | Unit I- Review of Microelectro nics and Introduction to MOS Technologies | K.Eshraghian<br>D,A.Pucknell | PHI        | 2005                         |

| 2    | Modern VLSI<br>Design                       | 2,3                      | Unit II-<br>Layout<br>Design and<br>Tools,Logic<br>Gates and<br>Layouts  | Wayne Wolf                   | Pearson    | 3 <sup>rd</sup> ed.,<br>1997 |

|      |                                             | 4                        | Unit III- Combination al Logic Networks Unit IV- Sequential              |                              |            |                              |

|      |                                             | 5<br>7,8                 | Systems Unit V-Floor Planning                                            |                              |            |                              |

# Code No: C0601, C5503, C7703, C6803, C5703, C7003, C4507, C3803 JAWAHARLAL NEHRU TECHNOLOGICAL UNIVERSITY HYDERABAD

## M.TECH I SEMESTER EXAMINATIONS, APRIL/MAY-2012 VLSI TECHNOLOGY AND DESIGN

Time: 3hours Max. Marks: 60 Answer any five questions

### All questions carry equal marks

---

- 1. Draw the circuits for n-MOS, p-MOS and C-MOS Inverter and explain about their operation and compare them.

- 2.a) Explain about scalable Design rules related to NMOS and CMOS Technologies.

- b) What are the issues involved in driving large capacitive loads in VLSI circuits? Explain.

- 3. Explain the following

- a) Why is n-diffusion to p-diffusion spacing is so large?

- b) Why metal metal spacing is larger than ploy-ploy spacing?

- c) What are the effects of scaling of  $V_t$ ?

- 4.a) Explain how to reduce the cross talk by using ground wire to minimize cross talk.

- b) Explain how fan-out and path delay influences delay in combinational networks.

- 5.a) What are various floor planning methods? Discuss in brief.

- b) Explain the delay in combinational logic network and how combinational delay can be reduced.

- 6.a) What are the various issues in system-on-chip design? Explain it briefly.

- b) Develop a sequence of tests for the '01' string recognizer which tests every combinational gate for both stuck -at -0 and stuck -at-1 faults.

- 7.a) Explain how the extracting a data path and controller from the ASM chart.

- b) Explain how would you translate a register transfer structure into a legal two phase latched sequential machine give an example.

- 8.a) Explain the sequential testing for testing a sequential machine and time-frame expansion of a sequential test.

- b) Write short notes on Chip design methodologies.

\* \* \* \*

# Code No: C3803, C0601, C7003, C5503, C7703, C4507, C6803, C5703 JAWAHARLAL NEHRU TECHNOLOGICAL UNIVERSITY HYDERABAD M.Tech I Semester Examinations, March-2011 VLSI TECHNOLOGY AND DESIGN

Time: 3hours Max. Marks: 60 Answer any five questions

#### All questions carry equal marks

b) Inductive interconnect delays.

1. a) What is latch-up condition in CMOS circuits? How it can be eliminated. What are the deficiencies of MOS technology? How do we over come them? [12] b) 2 a) explain the scalable design rules with equation b) Explain the pseudo-NMOS logic during the low to high transition. [12] 3 a) Explain the delay in combinational logic network and how combinational delay can be reduced. b) What are various switch logic circuits? Compare their merits and demerits. [12] 4. Explain about 1 -φ clocking rules for flip-flops and 2 -φ clocking disciplines for latches. [12] 5. a) What are various floor planning methods? Explain them clearly. b) With relevant diagrams explain about various Floor planning methods used in Layout design. [12] 6) a) Explain the technology independent and technology dependant strategies of logic optimization used in logic synthesis a) Explain briefly how the hardware/software Co-simulation and co-synthesis issued are addressed. [12] 7 a) Briefly explain the design validations in the floor planning. b) Describe the Placement and routing in floor planning. [12] 8. Write short notes of the following: a) power optimization.

[12]

# JAWAHARLAL NEHRU TECHNOLOGICAL UNIVERSITY HYDERABAD M. Tech I Semester Examinations, April/MAY-2012 VLSI TECHNOLOGY AND DESIGN (COMMON TO EMBEDDED SYSTEMS, VLSI SYSTEM DESIGN)

Time: 3hours Max. Marks: 60

Answer any five questions All questions carry equal marks

- - -

- 1. Design BiCMOS inverter with neat sketches and explain.

- 2. Explain Latch –up problem in CMOS circuits and discuss reducing methods.

- 3. Design a CMOS layout circuit for the function Y=((A+B).C.)?

- 4. Calculate K,H,50% delay of the Buffers required when a minimum size inverter drives a metal 1 Wire that is  $200 \lambda *3 \lambda$  in this case ,Ro=4.9k $\Omega$  and Co=0.69fF while Rint=5.34 $\Omega$  and cint=15fF+90.1fF=105.1fF.

- 5. Explain in detail about logic & Inter connect Designs with examples.

- 6. Explain LSSD with Latch example.

- 7.a) How ASAP & ALAP schedules are differ with data flow graph?

- b) Write any one of architectural method for reducing power consumption.

- 8. Explain a simple Dog Leg routing algorithm.

\*\*\*\*

#### Code No: D109115503

## JAWAHARLAL NEHRU TECHNOLOGICAL UNIVERSITY HYDERABAD M.Tech I Semester Regular Examinations March 2010 VLSI TECHNOLOGY AND DESIGN

(Common to Embedded Systems, Digital Systems & Computer Electronics, Digital Electronics & Communication Systems, VLSI System Design / VLSI / VLSI Design, Embedded Systems & VLSI Design, VLSI& Embedded Systems, Electronics & Communication Engineering, Systems & Signal Processing)

Time: 3hours

Max.Marks:60

## Answer any five questions All questions carry equal marks

- - -

- 1. a) Explain the fabrication procedure for P-Well CMOS technology.

- b) What are the differences between CMOS and BiCMOS technologies in fabrication?

- 2. a) Explain how to estimate propagation delay?

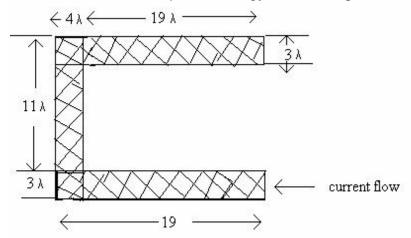

- b) Calculate the resistance of the polysilicon wire shown in figure. This polysilicon wire is to be fabricated with a 1 $\mu$ m technology. ( $R_s = 4\Omega/sq$ ).

- c) Determine  $Z_{pu}/Z_{pd}$  for NMOS inverter driven by another inverter.

- 3. a) Design a symbolic layout for a complementary CMOS circuit that implements  $F = \overline{A + BC}$ .

- b) What are the various properties of transmission gate logic?

- 4. a) What are various limitations of scaling?

- b) What is via? Why these are required in circuit design.

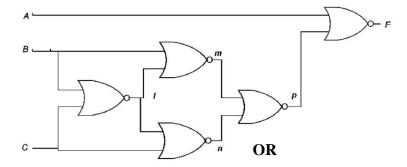

- 5. Consider the circuit shown in figure.

- i) Determine the logic function F.

- ii) Design a circuit to implement the same logic function using NOR gates.

- iii) Draw a transistor level schematic and use CMOS technology.

- 6. a) What is clock skew? How it is calculated?

- b) Explain how to optimize power for sequential circuits?

- 7. Explain Floor-Planning methods for a chip in detail.

- 8. Write short notes on

- a) Resistive and inductive interconnect delay.

- b) High level Synthesis.

\*\*\*\*

# JAWAHARLAL NEHRU TECHNOLOGICAL UNIVERSITY HYDERABAD M.Tech I SEMESTER EXAMINATIONS, APRIL/MAY-2013 VLSI TECHNOLOGY AND DESIGN

**Time: 3hours** Max.Marks:60

# **Answer any five questions**

|            | All questions carry equal marks                                                                                                                            |  |  |  |  |  |  |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

|            |                                                                                                                                                            |  |  |  |  |  |  |

|            | a) Explain the various steps of CMOS fabrication with neat diagrams.  Compare the CMOS and BiCMOS technologies.                                            |  |  |  |  |  |  |

| 2.         | Explain the following terms:                                                                                                                               |  |  |  |  |  |  |

|            | a) $g_m$ b) $G_{ds}$ c) $V_t$ d) $w_0$                                                                                                                     |  |  |  |  |  |  |

|            | What are different layout design rules? Explain them with suitable examples. What is wires and vias? How to design them.                                   |  |  |  |  |  |  |

| 4.a)<br>b) | Design a NOR gate using pass transistor logic. Derive the propagation delay $\tau_{PHL}$ for inverter.                                                     |  |  |  |  |  |  |

| 5.a)       | What are the different simulations available to test a combinational circuits? Explain them.                                                               |  |  |  |  |  |  |

| b)         | Draw the layout for CMOS NAND gate.                                                                                                                        |  |  |  |  |  |  |

| 6.a)<br>b) | Draw the circuit diagram of six transistor SRAM cell and explain its working. How power in sequential circuits is optimized? Explain any two such methods. |  |  |  |  |  |  |

| 7.a)<br>b) | What is Floor Planning? Explain it with examples. Explain the architecture for low power VLSI design.                                                      |  |  |  |  |  |  |

- Write short notes on the following:

a) High level synthesisb) Latch up. 8.

#### CPLD AND FPGA ARCHITECURES AND APPLICATIONS

#### **UNIT-I:**

#### **Introduction to Programmable Logic Devices:**

Introduction, Simple Programmable Logic Devices – Read Only Memories, Programmable Logic

Arrays, Programmable Array Logic, Programmable Logic Devices/Generic Array Logic; Complex

Programmable Logic Devices – Architecture of Xilinx Cool Runner XCR3064XL CPLD, CPLD

Implementation of a Parallel Adder with Accumulation.

#### **UNIT-II:**

#### **Field Programmable Gate Arrays:**

Organization of FPGAs, FPGA Programming Technologies, Programmable Logic Block Architectures,

Programmable Interconnects, Programmable I/O blocks in FPGAs, Dedicated Specialized Components of FPGAs, Applications of FPGAs.

#### **UNIT-III:**

#### **SRAM Programmable FPGAs:**

Introduction, Programming Technology, Device Architecture, The Xilinx XC2000, XC3000 and XC4000 Architectures.

#### **UNIT-IV:**

#### **Anti-Fuse Programmed FPGAs:**

Introduction, Programming Technology, Device Architecture, The Actel ACT1, ACT2 and

ACT3 Architectures.

#### **UNIT-V:**

#### **Design Applications:**

General Design Issues, Counter Examples, A Fast Video Controller, A Position Tracker for a Robot Manipulator, A Fast DMA Controller, Designing Counters with ACT devices, Designing Adders and Accumulators with the ACT Architecture.

#### **TEXT BOOKS:**

- 1. Field Programmable Gate Array Technology Stephen M. Trimberger, Springer International Edition.

- 2. Digital Systems Design Charles H. Roth Jr, Lizy Kurian John, Cengage Learning.

#### **REFERENCE BOOKS:**

- 1. Field Programmable Gate Arrays John V. Oldfield, Richard C. Dorf, Wiley India.

- 2. Digital Design Using Field Programmable Gate Arrays Pak K. Chan/Samiha Mourad, Pearson Low Price Edition.

- 3. Digital Systems Design with FPGAs and CPLDs Ian Grout, Elsevier, Newnes.

- 4. FPGA based System Design Wayne Wolf, Prentice Hall Modern Semiconductor Design.

# COURSE COVERAGE SUMMARY FOR CPLD & FPGA ARCHITECTURE

| S.N<br>o | TEXT BOOK<br>TITLE                               | Chapt<br>ers in<br>Text<br>Book | Units / Topics<br>Covered                                                                                                             | AUTHOR                                      | PUBLISHE<br>R             | EDITION |

|----------|--------------------------------------------------|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|---------------------------|---------|

| 1        | Digital System<br>Design                         | 2,3                             | Unit I-<br>Introduction to<br>Programmable<br>Logic Devices                                                                           | charles<br>H.Roth<br>jr,Lizy<br>Kurian john | cengage<br>learning       |         |

| 2        | Field<br>Programmable<br>GateArray<br>Technology | 2                               | Unit II-Field<br>Programmable<br>Gate Arrays<br>Unit III-SRAM<br>Programmable<br>FPGAs<br>Unit IV-Anti<br>Fuse<br>Programmed<br>FPGAs | Stephen<br>M.Trimberg<br>er                 | Springer<br>International |         |

|          |                                                  | 3                               | Unit V-Design<br>Applications                                                                                                         |                                             |                           |         |

#### **Code No: A5706**

# JAWAHARLAL NEHRU TECHNOLOGICAL UNIVERSITY HYDERABAD M.TECH I SEMESTER EXAMINATIONS, APRIL/MAY-2012 CPLD AND FPGA ARCHITECTURE AND APPLICATIONS (VLSI SYSTEM DESIGN)

Time: 3hours Max.Marks:60 Answer any five questions

#### All questions carry equal marks

- - -

- 1.a) Distinguish between ALTERA's CPLD and CYPRESS Flash 370 device.

- b) Compare the AMD's CPLD match 1 to 5.

- 2.a) Show the PLA implementation of a Binary adder of 4 bit.

- b) Explain about the ALTERA's third generation architecture of MAX7000 family with neat diagram.

- 3.a) Explain about the alternative realization for state machine using micro programming.

- b) Explain about the top-down design approach of state machine with an example.

- 4.a) Explain about one hot state machine with state table and state diagrams.

- b) Develop one hot state diagram for a sequence checker whose output is '1' whenever the sequence 0101 is detected. Also specify its Transition Table.

- 5.a) Explain the extended petrinets for parallel controllers

- b) Explain about linked state machine for a dice game.

- 6.a) Explain about the datapath and functional partition of FSM system level design

- b) Design a binary multiplier control using one-hot method.

- 7. Explain the complete design flow to implement a 4 bit Ripple-carry adder circuit on to FPGA using an EDA tool. Also explain the timing simulation for the same.

- 8. Write a brief note on any two:

- a) Floor plan

- b) Optimized reconfigurable cell array.

- c) Speed performance of different CPLDs.

\*\*\*\*\*

# Code No: C6106, C0608, C7702, C6802, C5702, C6506 JAWAHARLAL NEHRU TECHNOLOGICAL UNIVERSITY HYDERABAD M.TECH I SEMESTER EXAMINATIONS APRIL/MAY-2012

# **CPLD & FPGA ARCHITECTURES AND APPLICATIONS Time: 3hours Max.Marks:60 Answer any five questions**

#### All questions carry equal marks

- - -

- 1.a) Explain the PLA design for the fallowing f=x'y'z+x'yz+xyz+xy'z'.

- b) Explain speed performance and system programming.

- 2. Consider any logic block and explain routing architecture.

- 3. Explain the design flow technology mapping for FPGA's.

- 4. Explain state machine chart using micro programming linked state machine.

- 5. Explain hot state machine with an example.

- 6. Explain the front end and dsign tools for FPGA.

- 7. Explain the design flow using FPGA's.

- 8. Write short notes on the following

- i) Design of parallel adder cell.

- ii) Sequential circuit.

- iii) Parallel controllers.

\*\*\*\*

# Code No: C6106, C0608, C7702, C6802, C5702, C6506 JAWAHARLAL NEHRU TECHNOLOGICAL UNIVERSITY HYDERABAD M.Tech I Semester Examinations March/April-2011 CPLD & FPGA ARCHITECTURES AND APPLICATIONS (COMMON TO COMMUNICATION SYSTEMS, DIGITAL SYSTEMS & COMPUTER ELECTRONICS, EMBEDDED SYSTEMS & VLSI DESIGN, VLSI&EMBEDDED SYSTEMS, VLSI SYSTEM DESIGN, WIRELESS & **MOBILE COMMUNICATIONS**) **Time: 3hours** Max.Marks:60 Answer any five questions

All questions carry equal marks

| <ol> <li>a. Explain the design of altera flex logic -1000 series cpld.</li> <li>b. Explain The Pla Design With An Example.</li> </ol>     | [12]   |

|-------------------------------------------------------------------------------------------------------------------------------------------|--------|

| 2. Explain Cypres Flash 370 Device Technology.                                                                                            | [12]   |

| 3. a. Explain the fpga with channel and channel less gate array. Explain retechnique implemented.                                         | outing |

| b. Explain the design aspects of altera's flex 8000 fpga.                                                                                 | [12]   |

| <ul><li>4. Explain the microprograming linked state machine with an example.</li><li>5. a. Explain the properties of petrinets.</li></ul> | [12]   |

| b. Explain the state machine for petrinets with an example.                                                                               | [12]   |

| 6. Explain the design flow using fpga mentor graphics eda tool.                                                                           | [12]   |

| 7. Design a parallel adder sequential circuit.                                                                                            | [12]   |

| 8. Write short notes on the following.                                                                                                    |        |

| i. Speed performance of actel.                                                                                                            |        |

| <ul><li>ii. Speed performance in system programmability.</li><li>iii. Asic design flow.</li></ul>                                         | [12]   |

\*\*\*\*

#### Code No: D109110608

## JAWAHARLAL NEHRU TECHNOLOGICAL UNIVERSITY HYDERABAD M.Tech I Semester Regular Examinations March/April 2010 CPLD& FPGA ARCHITECTURES AND APPLICATIONS

(COMMON TO DSCE, WIRELESS & MOBILE COMMUNICATION, VLSI SYSTEM DESIGN/VLSI/VLSI DESIGN, COMMUNICATION SYSTEMS, EMBEDDED SYSTEMS & VLSI DESIGN, VLSI & EMBEDDED SYSTEMS)

Time: 3hours Max.Marks:60 Answer any five questions

#### All questions carry equal marks

- - -

- 1. (a). Draw and explain architecture of PLD.

- (b). With diagram explain Functional block.

- 2. (a). Explain Architecture of Altera MAX 5000 series CPLD.

- (b). Explain the ACT 2 and ACT 3 Logic Modules.

- 3. (a). Draw and explain the General Block diagram of FPGA.

- (b). Discuss Speed performance of different FPGAs.

- 4. (a). Write short note on extended Petri nets for parallel controllers.

- (b). Explain about One Hot State machine.

- 5. (a). Explain Basic concepts of Petri nets for state machines.

- (b). Explain briefly about Front end Design tools for ASICs.

- 6. Explain in detail about Design flow using FPGAs.

- 7. (a). Explain about Parallel Adder Cell.

- (b). Briefly explain about Serial Multiplier with Parallel Addition.

- 8. Write short notes on any TWO of the following:

- (i). EDA tools

- (ii). Speed performance of different

CPLDs. (iii). Applications of CPLDs

\*\*\*\*\*

Code No: A5706 NR

# JAWAHARLAL NEHRU TECHNOLOGICAL UNIVERSITY HYDERABAD M.Tech I Semester Regular Examinations March 2010 CPLD AND FPGA ARCHITECTURE AND APPLICATIONS (VLSI SYSTEM DESIGN)

Time: 3hours Max.Marks:60

# Answer any five questions All questions carry equal marks

- - -

- 1.a) Compare Altera FLEX Logic-10000 series CPLD with Cypres FLASH 370 device technology.

- b) What are complex programmable logic devices? Briefly outline salient features of these devices and applications.

- 2.a) How many macrocells available in these CPLDs:

- i) EPM 7032

- ii) EPM 7064

- iii) EPM 7128S

- iv) EPM7160S.

- b) Briefly state the difference between CPLPs having sum-of-products architecture and look up table architecture.

- 3.a) State the possible preset configurations of a MAX7000s.

- b) What can be done with the macrocells in LAB that are not connected to I/O pins?

- c) Draw a neat block schematic of a logic element of FLEX10000.

- 4.a) Give examples of fuse link in an array logic for a CPLD.

- b) What are the possible structures of the CLBs? Draw the structures.

- 5.a) Compare the ACTEL's Act-1,2,3 performance.

- b) Design a 4 bit Ripple counter using one-hot state machine.

- 6. Design a digital system which performs a binary multiplication using Asm chart and design the controller of their system. Implement the same using PLA.

- 7. Explain the complete design flow to implement a Ripple-carry adder circuit on to FPGA using an EDA tool. Also explain the timing simulation for the same.

- 8. Write a brief note on:

- a) Floor plan

- b) Mentor graphic EDA tool "FPGA Advantage".

\*\*\*\*\*

#### MICROCONTROLLERS FOR EMBEDDED SYSTEM DESIGN

#### UNIT -I: ARM Architecture:

ARM Design Philosophy, Registers, Program Status Register, Instruction Pipeline, Interrupts and Vector Table, Architecture Revision, ARM Processor Families.

UNIT –II:ARM Programming Model – I:

Instruction Set: Data Processing Instructions, Addressing Modes, Branch, Load, Store

Instructions, PSR Instructions, Conditional Instructions.

UNIT -III:ARM Programming Model - II:

Thumb Instruction Set: Register Usage, Other Branch Instructions, Data Processing Instructions, Single-Register and Multi Register Load-Store Instructions, Stack, Software Interrupt Instructions

UNIT –IV:ARM Programming:

Simple C Programs using Function Calls, Pointers, Structures, Integer and Floating Point Arithmetic, Assembly Code using Instruction Scheduling, Register Allocation, Conditional Execution and Loops.

UNIT –V:Memory Management:

Cache Architecture, Polices, Flushing and Caches, MMU, Page Tables, Translation, Access Permissions, Context Switch.

#### TEXT BOOKS:

1. ARM Systems Developer's Guides- Designing & Optimizing System Software – Andrew N. Sloss, Dominic Symes, Chris Wright, 2008, Elsevier.

#### REFERENCE BOOKS:

3. Embedded Microcomputer Systems, Real Time Interfacing – Jonathan W. Valvano – Brookes / Cole, 1999, Thomas Learning.

# **COURSE COVERAGE SUMMARY**

# MICROCONTROLLERS FOR EMBEDDED SYSTEM DESIGN

| S.No | TEXT BOOK   | Chapters | Units / Topics | AUTHOR    | PUBLISHER | EDITION |

|------|-------------|----------|----------------|-----------|-----------|---------|

|      | TITLE       | in Text  | Covered        |           |           |         |

|      |             | Book     |                |           |           |         |

| 1    | ARM Systems | 1,2      | I-ARM          | Andrew N. | Elsevier  | 2008    |

|      | Developers  |          | Architecture   | Sloss,    |           |         |

|      | Guides-     | 3        | Unit II- ARM   | Dominic   |           |         |

|      | Design &    |          | Programming    | Symes,    |           |         |

|      | Optimizing  |          | Model-I        | Chris     |           |         |

|      |             |          |                |           |           |         |

|      | System      | 4        | Unit III- ARM  | Wright,   |           |         |

|      | Software    |          | Programming    |           |           |         |

|      |             |          | Model-II       |           |           |         |

|      |             |          |                |           |           |         |

|      |             | 5,6      | Unit IV- ARM   |           |           |         |

|      |             |          | Programming    |           |           |         |

|      |             | 12       | Unit-Memory    |           |           |         |

|      |             |          | Management     |           |           |         |

#### Code No: C3806, C0604, C7006, C5501, C7701, C5701, C6801

## JAWAHARLAL NEHRU TECHNOLOGICAL UNIVERSITY HYDERABAD M.TECH I - SEMESTER EXAMINATIONS, APRIL/MAY-2012

#### MICROCONTROLLERS FOR EMBEDDED SYSTEM DESIGN

#### (COMMON TO VLSI SYSTEM DESIGN, VLSI & EMBEDDED SYSTEMS)

Time: 3hours Max. Marks: 60 Answer any five questions

#### All questions carry equal marks

- - -

- 1.a) Explain the hardware units and devices in an Embedded system.

- b) Give the classification of embedded systems.

- 2.a) Discuss in detail the architecture of 8051 microcontroller.

- b) Explain the need for counters.

- 3. Discuss in detail memory and I/O devices interfacing to the microcontroller.

- 4.a) Compare Continuous timer blocks and Switched capacitor blocks.

- b) Draw the architecture of Programmable system-on-chip.

- 5.a) Explain in detail the architecture of Embedded RISC processor.

- b) Explain the modes of operation of ARM processor.

- 6.a) Explain the following terms:

- i) Context switch

- ii) Interrupt latency

- b) Explain the device drivers for internal programmable timing devices.

- 7. Describe the following:

- a) Serial communication protocols b) SDMA

- 8. Write notes on the following: a)

Embedded software

- b) I/O ports

- c) Digital blocks.

\* \* \* \* \* \*

#### Code No: C3806, C0604, C7006, C5501, C7701, C5701

#### JAWAHARLAL NEHRU TECHNOLOGICAL UNIVERSITY HYDERABAD

#### M.Tech I - Semester Examinations, October/November-2011

#### MICROCONTROLLERS FOR EMBEDDED SYSTEM DESIGN

(COMMON TO DIGITAL ELECTRONICS & COMMUNICATION SYSTEMS, DIGITAL SYSTEMS & COMPUTER ELECTRONICS, ELECTRONICS & COMMUNICATION ENGINEERING, EMBEDDED SYSTEMS, EMBEDDED SYSTEMS & VLSI DESIGN, VLSI SYSTEM DESIGN)

Time: 3hours Max. Marks: 60 Answer any five questions

#### All questions carry equal marks

|          | 1  | a. What is an Embedded system? How is it different from a personal computer | er?      |

|----------|----|-----------------------------------------------------------------------------|----------|

|          |    | •                                                                           | 4M       |

| b.<br>2. | a. | r · · · · · · · · · · · · · · · · · · ·                                     | 8M<br>8M |

|          | b. | Discuss the need for Timers.                                                | 4M       |

| 3.       | a. | Write notes on the various Memory arbitration schemes.                      | 6M       |

|          | b. | Explain about PIC controllers.                                              | 6M       |

| 4.       | a. | Discuss in detail PSOC architectures.                                       | 8M       |

|          | b. | Explain about Digital blocks.                                               | 4M       |

| 5.       |    | Explain the Register set and instructions of ARM processor.                 | 12M      |

|          | a. | What is context switch? When does it take place?                            | 4M       |

|          | b. | Explain in detail serial port device driver.                                | 8M       |

| 7.       | a. | Explain in detail the Ethernet protocol.                                    | 6M       |

|          | b. | Discuss about the External bus interface.                                   | 6M       |

|          |    | Write short notes on the following:  Formalization of system design  4      | M        |

|          | i  | i. PIC Controllers 4                                                        | M        |

|          | I  | nterrupt latency. 4                                                         | M        |

# JAWAHARLAL NEHRU TECHNOLOGICAL UNIVERSITY HYDERABAD

# $M. Tech\ I\ -\ Semester\ Examinations, March/April-2011$

# MICROCONTROLLERS FOR EMBEDDED SYSTEM DESIGN

Time: 3hours Max. Marks: 60

# Answer any five questions

# All questions carry equal marks

| 1.a)     | What are the issues in designing embedded system?                                                                                  |                |

|----------|------------------------------------------------------------------------------------------------------------------------------------|----------------|

| b)       | Why does a processor system always need an interrupt handle?                                                                       | [6+6]          |

| 2.a)     | Explain the need of a watchdog times and reset after the watched time.                                                             |                |

| b)       | What are the advantages of an ASIP for design of an embedded system?                                                               | [6+6]          |

| 3.       | Explain the serial communications control operation in 8051 in different modes of                                                  | f              |

|          | operation.                                                                                                                         | [12]           |

| 4.a) I   | Draw a neat program model of ARM and explain its different modes of usage.                                                         |                |

| b) I     | Explain the multiple register transfer instruction set of ARM processor.                                                           | [6+6]          |

| 5.a)     | Explain events management? How are inter-task communication objects used for communication and synchronization?                    |                |

| b)       | How do we choose scheduling strategy for the periodic, a periodic and sporadic ta                                                  | ısks?<br>[6+6] |

| 6.a)     | How do you create a counsiling semaphore?                                                                                          |                |

| b)<br>c) | How do we initiate round robin time series scheduling?<br>How do you let a lower priority task executes in a preemptive scheduler? | [6+6]          |

| 7.a)     | Discuss about I2C bus communication with its devices.                                                                              |                |

| b)       | How does CAN differ from I2C?                                                                                                      | [6+6]          |

| 8.       | Write brief note on:                                                                                                               |                |

|          | a) SDMA                                                                                                                            |                |

|          | b) Continuous timer blocks in PSOC.                                                                                                | [12]           |

|          | 00000                                                                                                                              |                |

--ooOoo--

# JAWAHARLAL NEHRU TECHNOLOGICAL UNIVERSITY HYDERABAD M.Tech I SEMESTER EXAMINATIONS, APRIL/MAY-2013

# MICROCONTROLLERS FOR EMBEDDED SYSTEM DESIGN

#### (EMBEDDED SYSTEMS)

Time: 3hours Max.Marks:60

#### Answer any five questions. All questions carry equal marks

- 1.a) Explain different Hardware units in Embedded systems.

- b) Explain the design process for an embedded application.

- c) Explain how embedded systems are classified.

- 2.a) Explain the memory mapped I/O and I/O mapped I/O.

- b) Explain how 8051 is interfaced to external memory.

- c) What are the different timers in 8051 and its modes?

- Explain the ARM processor

- 3.a) architecture.

- Give overview of programmable system on chip b) (PSOC).

- 4.a) Explain context switching with an example. What is Pre-emptive scheduling?

- b) Explain the procedure to write a device driver using interrupt service routine.

- 5. Explain serial communication protocols with an example.

- 6. A)What is the difference between RISC and CISC Architecture?

- b) Explain continuous timer blocks and switched capacitor blocks.

- 7. Explain PIC ontrollers.

- 8. Write short notes on the following:

- a) Ethernet protocol.

- b) ARM6TDMI based embedded system.

#### **DIGITAL SYSTEM DESIGN**

#### (ELECTIVE -I)

#### **UNIT -I: Minimization and Transformation of Sequential Machines:**

The Finite State Model – Capabilities and limitations of FSM – State equivalence and machine minimization – Simplification of incompletely specified machines.

Fundamental mode model – Flow table – State reduction – Minimal closed covers – Races, Cycles and Hazards.

#### **UNIT -II:Digital Design:**

Digital Design Using ROMs, PALs and PLAs, BCD Adder, 32 – bit adder, State graphs for control circuits, Scoreboard and Controller, A shift and add multiplier, Array multiplier, Keypad Scanner, Binary divider.

#### **UNIT -III:SM Charts:**

State machine charts, Derivation of SM Charts, Realization of SM Chart, Implementation of Binary Multiplier, dice game controller.

### **UNIT -IV:Fault Modeling & Test Pattern Generation:**

Logic Fault model – Fault detection & Redundancy- Fault equivalence and fault location –Fault

dominance – Single stuck at fault model – Multiple stuck at fault models –Bridging fault model.

Fault diagnosis of combinational circuits by conventional methods – Path sensitization techniques, Boolean Difference method – Kohavi algorithm – Test algorithms – D algorithm, PODEM, Random testing, Transition count testing, Signature analysis and test bridging faults.

#### **UNIT -V:Fault Diagnosis in Sequential Circuits:**

Circuit Test Approach, Transition Check Approach – State identification and fault detection experiment, Machine identification, Design of fault detection experiment

#### **TEXT BOOKS:**

- 1. Fundamentals of Logic Design Charles H. Roth, 5 th Ed., Cengage Learning.

- 2. Digital Systems Testing and Testable Design Miron Abramovici, Melvin A.

Breuer and Arthur D. Friedman- John Wiley & Sons Inc.

3. Logic Design Theory – N. N. Biswas, PHI

#### **REFERENCE BOOKS:**

- 1. Switching and Finite Automata Theory Z. Kohavi , 2 nd Ed., 2001, TMH

- 2. Digital Design Morris Mano, M.D.Ciletti, 4 th Edition, PHI.

- 3. Digital Circuits and Logic Design Samuel C. Lee , PHI

# DIGITAL SYSTEM DESIGN

# **COURSE COVERAGE SUMMARY**

| S.No | TEXT            |                | AUTHOR(S)    |              | EDITION   |

|------|-----------------|----------------|--------------|--------------|-----------|

|      | BOOK            | Units / Topics |              |              |           |

|      | TITLE           | Covered        |              | PUBLISHERS   |           |

| 1    | Fundamentals    |                | Charles H.   |              | 5 th Ed.  |

|      | of Logic        |                | Roth         | Cengage      |           |

|      | Design          | I,II           |              | Learning     |           |

| 2    |                 |                | Miron        |              |           |

|      | Digital         |                | Abramovici,  |              |           |

|      | Systems         |                | Melvin A.    |              |           |

|      | Testing and     |                | Breuer and   | John Wiley & |           |

|      | Testable        |                | Arthur D.    | Sons Inc.    |           |

|      | Design          | IV             | Friedman     |              |           |

| 3    | . Logic Design  | III,IV         |              | PHI          |           |

|      | Theory          |                | N. N. Biswas |              |           |

| 4    | . Switching and | V              |              | TMH          | 2 nd Ed., |

|      | Finite          |                |              |              | 2001      |

|      | Automata        |                |              |              |           |

|      | Theory          |                | Z. Kohavi    |              |           |

**Code No: 5106B**

**R13**

#### JAWAHARLAL NEHRU TECHNOLOGICAL UNIVERSITY HYDERABAD

#### M.Tech I Semester Examinations, February - 2014

#### DIGITAL SYSTEM DESIGN

(Digital System and Computer Electronics)

Time: 3 Hours Max. Marks: 60

#### **Instructions:**

i) Part A is compulsory Question for 20 marks.

ii) Part B consists of five questions with "either" "or" pattern. The student has to answer any one. However students have to answer five questions from Part B (numbered from 2 to 6)

#### **PART - A (Answer all sub questions)**

#### $5 \times 4 \text{ marks} = 20$

- 1.a) Define Race, also explain the terms critical race and non critical race.

- b) Implement a full adder using PAL

- c) Draw and explain different components of an SM chart.

- d) Draw the circuit which realizes the function  $f(x) = x_1x_2 + x_3 x_4$  using AND- OR gates using Boolean difference method obtain the test set to detect SA0 fault on input line  $x_1$  of the circuit.

- e)Write the rules to construct a distinguishing sequence of a machine

# **PART – B** $5 \times 8$ marks = 40 Answer either "a" or "b" from each question

2.a) Define flow table . Obtain flow table for a sequential circuit with two inputs  $x_1$  and  $x_2$  and one output z for the following data. The initial input state is  $x_1 = x_2 = 0$ . The output value is to be 1 if and only if the input state is  $x_1 = x_2 = 1$  and the preceding input state is  $x_1 = 0$ ,  $x_2 = 1$ .

#### OR

b) Classify hazards and implement the following Boolean function by a hazard free OR-AND network  $f=\sum (0,2,6,7)$ .

3.a) Realize a 4-bit BCD to gray code converter using PLA.

#### OR

- b) Draw the block diagram of a parallel binary divider and obtain the state graph for divider control circuit.

- 4.a) Derive the state machine chart for a binary multiplier and realize using a PLA.

#### OR

- b)Derive the state machine chart for a dice controller.

- 5.a) Apply PODEM algorithm to derive a test to detect a l s-a-1 fault for the combinational circuit shown below.

- b) Explain signature analysis technique using an example.

- 6.a) Explain fault detection in a sequential circuit using circuit test approach with an example.

#### OR

c) i) What is a homing sequence? Write the rules to construct a homing sequence of machine.

ii) Conduct a homing experiment and determine final state of the given machine

Machine M<sub>1</sub>

Next State

| Present State | X=0 | x=1 |

|---------------|-----|-----|

| A             | B,0 | D,0 |

| В             | A,0 | B,0 |

| C             | D,1 | A,0 |

| D             | D,1 | C,0 |

### Code No: A0601, A5701

## JAWAHARLAL NEHRU TECHNOLOGICAL UNIVERSITY HYDERABAD

# M.Tech I Semester Examinations, March/April 2011

#### **DIGITAL SYSTEM DESIGN**

Time: 3hours Max. Marks: 60

# Answer any five questions All questions carry equal marks

- - -

- 1.a) Draw the state diagram, state table and ASM chart for a D Flip-Flop.

- b Discuss the different components of ASM chart.

[12]

2.a) Implement the logic function 'F' using ROM

$$F = \overline{ABC + ABC + ABC + ABC}$$

b Explain how a sequential circuit can be designed using CPLD?

[12]

- 3.a) Show that the three paths indicated in the circuit as shown in Fig. 1 cannot be sensitized individually but can be sensitized simultaneously.

- b) Classify faults and give some examples to each class.

[12]

- 4.a) Write a D Algorithm and compare it with other test pattern generation methods.

- b) How signature analysis is used for testing bridging faults?

[12]

5. Consider the machine whose transition table is given in table shown in Fig 2. Design a checking experiment for this machine. [12]

| q × | а    | b    | С    | d    |

|-----|------|------|------|------|

| Α   | Α, 0 | B, 1 | Α, 0 | D, 1 |

| В   | C, 1 | Α, 0 | В, 0 | Α, 0 |

| С   | D, 1 | B, 1 | A, 1 | В, 0 |

| D   | В, о | C, 1 | A, 1 | C, 1 |

Fig: 2

- 6.a) What is PLA folding? Why it is needed?

- b) Implement the following three Boolean functions with a PLA.  $F_1(A, B, C) = \varepsilon(0,1,2,4)$

$$F_2(A, B, C) = \varepsilon(0, 5, 6, 7)$$

$$F_3(A, B, C) = \varepsilon(0, 3, 5, 7)$$

[12]

- 7. Explain how to test a PLA circuits? [12]

- 8.a) Draw & Explain the Basic model of sequential circuit.

- b) Give a state assignment without critical races to each of the following asynchronous machine shown in figure 3. [12]

| q X | 10  | I <sub>1</sub> | 12       | 13           |

|-----|-----|----------------|----------|--------------|

| Α   | (A) | С              | (A)      | В            |

| В   | Α   | <b>B</b>       | Α        | $\bigcirc$ B |

| С   | (C) | (C)            | E        | D            |

| D   | С   | В              | <b>D</b> | <b>D</b>     |

| E   | E   | F              | <b>E</b> | D            |

| F   | E   | (F)            | Α        | В            |

#### CMOS ANALOG INTEGRATED CIRCUIT DESIGN

#### UNIT -I:

MOS Devices and Modeling:

The MOS Transistor, Passive Components- Capacitor & Resistor, Integrated circuit Layout, CMOS Device Modeling - Simple MOS Large-Signal Model, Other Model Parameters, Small-Signal Model for the MOS Transistor, Computer Simulation Models, Sub-threshold MOS Model.

#### UNIT -II:

**Analog CMOS Sub-Circuits:**

MOS Switch, MOS Diode, MOS Active Resistor, Current Sinks and Sources, Current Mirrors-Current mirror with Beta Helper, Degeneration, Cascode current Mirror and Wilson Current Mirror, Current and Voltage References, Band gap Reference.

#### UNIT -III:

**CMOS** Amplifiers:

Inverters, Differential Amplifiers, Cascode Amplifiers, Current Amplifiers, Output Amplifiers, High Gain Amplifiers Architectures.

#### UNIT -IV:

**CMOS Operational Amplifiers:**

Design of CMOS Op Amps, Compensation of Op Amps, Design of Two-Stage Op Amps, Power-Supply Rejection Ratio of Two-Stage Op Amps, Cascode Op Amps, Measurement Techniques of OPAmp.

#### UNIT -V:

Comparators:

Characterization of Comparator, Two-Stage, Open-Loop Comparators, Other Open-Loop Comparators, Improving the Performance of Open-Loop Comparators, Discrete-Time Comparators.

#### TEXT BOOKS:

- 1. CMOS Analog Circuit Design Philip E. Allen and Douglas R. Holberg, Oxford University Press, International Second Edition/Indian Edition, 2010.

- 2. Analysis and Design of Analog Integrated Circuits- Paul R. Gray, Paul J. Hurst, S. Lewis and R. G. Meyer, Wiley India, Fifth Edition, 2010.

#### REFERENCE BOOKS:

- 1. Analog Integrated Circuit Design- David A. Johns, Ken Martin, Wiley Student Edn, 2013.

- 2. Design of Analog CMOS Integrated Circuits- Behzad Razavi, TMH Edition.

- 3. CMOS: Circuit Design, Layout and Simulation-Baker, Li and Boyce, PHI.

# COURSE COVERAGE SUMMARY CMOS ANALOG INTEGRATED CIRCUIT DESIGN

| S.No | TEXT           | Units /   | AUTHOR(S)           |            | EDITION        |

|------|----------------|-----------|---------------------|------------|----------------|

|      | BOOK           | Topics    |                     | PUBLIS     |                |

|      | TITLE          | Covered   |                     | HERS       |                |

| 1    |                |           |                     |            | Internationa   |

|      |                |           |                     |            | 1 Second       |

|      |                |           |                     |            | Edition/Indi   |

|      |                |           |                     | Oxford     | Lamon/mar      |

|      |                |           | Philip E. Allen and |            | on Edition     |

|      | CMOS Analog    |           | Douglas R.          | University | an Edition,    |

|      | Circuit Design | I-V       | Holberg             | Press      | 2010           |

| 2    | Analysis and   |           |                     |            | 4. Fifth       |

|      | Design of      |           |                     |            | Edition, 2010. |

|      | Analog         |           | Paul R. Gray, Paul  | 3. Wiley   |                |

|      | Integrated     |           | J. Hurst, S. Lewis  | India,     |                |

|      | Circuits-      | I,II      | and R. G. Meyer     |            |                |

| 3    | Analog         | II,III,IV |                     | Wiley      | 2013           |

|      | Integrated     |           | David A. Johns,     | Student    |                |

|      | Circuit Design |           | Ken Martin          | Edn        |                |

#### SEPTEMBER-2009 PAPER-SUPPLEMENTARY

- 1.a] Why is emitter resistor RE replaced by a constant current bias circuit in differential amplifier stage of an op-AMP?

- b] Design the dual input balanced output differential amplifier with the current mirror bias (shown below) according to the following specifications:

- i) Supply voltage  $Vs = \pm 12V$

- ii) Maximum output voltage swing 6Vpp.

- 2.a] Briefly explain the need for compensating networks in op-Amps.

- b] Explain in detail about advanced current mirror compensating network.

- 3.a] What is a comparator? List the important characteristics of the comparator.

- b] Explain different types of comparators with neat circuit diagrams.

- 4.a] Explain about CMOS sample and Hold circuit with neat waveforms.

- b] Design a second order Butterworth low pass filter with a cutoff frequency of 500 Hz and a pass band gain of -2. Assume that a  $5V \pm$  power supply and a CMOS clock are used. [Using MF5].

- 5.a] Give the procedure of design of Biquard switched capacitor filter. [ filter is a low pass filter].

- b] Explain the operation of switched capacitor gain circuit.

- 6.a) What is difference between A/D and D/A converters? Give one application of each.

- b] Draw and explain the Nyquist rate D/A converter using binary sealed converter.

- 7.a] Compare the performance of different types of D/A converters?

- b] Define the resolution, settling time and conversion time of D/A converters.

- c] Explain the operation of cycle flash type A/D converter with a neat circuit diagram.

- 8.a) Write the differences b/w continuous time and discrete time filters.

- b] Explain in detail about digital decimation filter.

#### MARCH-2009-PAPER-(REGULAR)

- 1.a) Deduce the small signal model for an n-channel MOSFET taking into account the body effect.

- b) Justify the choice of pmos loads.

- Discuss the design aspects of CMOS source follower and derive an expression for the gain.

- b) Consider a source follower which is biased by a current mirror. The dimensions of all the transistors are  $100\,\mu\,\text{m}/1.6\,\mu\,\text{m}$ ,  $\mu_{\rm n}C_{\rm ax}=90\,\mu A/V^2$ ,  $\mu_{\rm p}C_{\rm ax}=30\,\mu A/V^2\,\mathrm{l_{bias}=100}$   $\mu\,\text{A}$ ,  $\gamma_{\rm n}=0.5V^{1/2}$ ,  $r_{\rm ak-n}=8000\,L(\mu m)/I_{\rm D}(mA)$ . What is the gain of the stage?

- 3.a) State the limitations of single stage amplifiers.

- b) Explain in detail the design and operation of cascade current mirror. Identify the limitations and suggest remedies.

- 4.a) Deduce the necessary condition that ensures zero input-offset voltage for a 2 stage OP amp.

- b) Discuss the trade offs involved in selecting the input stage as p-channel or n-channel with respect to a 2 stage OP amp.

- 5. Discuss in detail the compensation of OP amp that makes it completely independent of process and temperature variations.

- 6.a) Discuss in detail the design features of fully differential folded cascade op amp.

- b) Give an account of charge injection errors in connection with comparators and suggest a method to minimize the same.

- 7.a) Explain the following in the context of data converters:

- i) Resolution

- ii) Offset and gain error

- iii) Accuracy

- iv) Differential non linearity error

- v) Monotonicity

- b) Explain briefly a 3 bit flash A/D converter. State the salient issues in designing flash A/D converters.

- 8.a) Show that the dynamic range can be increased by over sampling.

- b) Discuss the stability and linearity issues associated with delta sigma converters.

#### MARCH-2008 PAPER-(REGULAR)

- 1.a) Explain large signal modelling of single stage BJT amplifier with neat sketches.

- b) Explain common source amplifier with current mirror active load.

- 2.a) Explain the effect of negative feedback on the frequency response of OP-AMP.

- b) Explain about cascode (or) CE-CB operational amplifier and obtain AC analysis of it.

- 3.a) Explain about charge injection error.

- b) With a neat circuit diagram explain Bi-CMOS comparator.

- c) Write the comparisons between Latched and Bi-CMOS comparators.

- 4.a) What is a switched capacitor filter? List important features of it. How does it differ from an analog filter?

- b) Explain the operation of Bimos sample and Hold circuit with neat waveforms.

- 5.a) Explain the operation of switched capacitor circuit with neat waveforms.

- b) Briefly explain correlated double sampling techniques.

- 6.a) What is Quantization Noise? Explain in detail.

- b) Explain the operation at D/A converters using Hybrid converter.

- 7.a) What are the performance limitations of converters?

- b) Compare different types of A/D converters.

- c) Explain Successive Approximation A/D converter with a neat circuit diagram.

- 8.a) What is over sampling? Explain over sampling with and without noise sampling.

- b) Explain in detail about Band pass over sampling converter.

#### **FEBRUARY-2007 PAPER**

- Derive an expression for the -3dB frequency of a bipolar CE amplifier.

- b) In a CMOS source follower circuit all transistors have  $W/L = 100 \mu m, /1.6 \mu m \ \mu_n C_{ox} = 90 \mu A/V^2, \ \mu_p C_{ox} = 30 \mu A/V^2, \ I_{bias} = 100 \mu A, \ r_n = 0.5 V^{1/2}, \ v_{ds-n}{}^{(\Omega)} = 8000 L \ (\mu m)/ID(mA).$  Determine the gain of the stage.

- 2.a) Draw the circuit of CMOS current mirror and explain its working principle.

- b) Explain why source/emitter follower circuits exhibits large amounts of overshoot and ringing.

- 3.a) What are the ways of improving slew rate of 2-stage CMOS opamp? And derive an expression for slew rate of CMOS opamp.

- b) Explain about various OPAMP compensation techniques.

- 4.a) What is CMFB circuit? What are various methods of designing CMFB circuits? And compare them.

- b) Explain the principle of continuous time CMFB circuit.

- 5.a) Briefly explain about various performance parameters of sample-and-hold circuit.

- b) Draw the circuit of switched capacitor circuit and explain its principle.

- 6.a) Compare and contrast CMOS and BICMOS sample and hold circuits and their performance.

- b) Define the terms as referred to converters:

- i) offset and gain error

- ii) INL error

- iii) DNL error

- iv) Sampling time uncertainty.

- 7.a) Prove that the sinusoidal signal has 1.76dB more power than a random signal which is uniformly distributed.

- b) Explain the principle of operation of dual slope A/D converter.

- 8.a) What are the advantages of 1-bit D/A converters?

- b) Derive the component values of 1st order continuous time filter.

#### **SEPTEMBER-2008 PAPER-(SUPPLEMENTARY)**

- 1.a) Derive an expression for gm of an N-channel MOS FET operating in linear and saturation regions.

- b) Give the relative performance of CS, CG, CD amplifiers.

- Discuss the design aspects of CMOS common source amplifier with diode connected load and derive an expression for the gain.

- b) Consider a source follower which is biased by a current mirror. The dimensions of all the transistors are  $100\mu m/1.6\mu m$ ,  $\mu_n C_{ax} = 90\mu A/V^2$ ,  $\mu_p C_{ax} = 30\mu A/V^2 I_{bias} = 100\mu A$ ,  $\gamma_n = 0.5 V^{1/2}$ ,  $r_{ds-n} = 8000 L(\mu m)/I_D(mA)$ . What is the gain of the stage?

- 3.a) State the limitations of single stage amplifiers.

- b) Explain in detail the design and operation of Wilson current mirror.

- 4.a) Deduce the necessary condition that ensures zero input-offset voltage for a 2 stage OP amp.

- b) Discuss the trade offs involved in selecting the input stage as p-channel or n-channel with respect to a 2 stage OP amp.

- 5.) Discuss in detail the compensation of OP amp that makes it completely independent of process and temperature variations.

- 6.a) Give the significance of CMFB circuits.

- b) Give an account of charge injection errors in connection with comparators and suggest a method to minimize the same.

- 7.a) Explain the following in the context of data converters:

- i) Resolution

- ii) Offset and gain error

- iii) Accuracy

- iv) Integral non linearity error

- v) Missing codes

- b) Explain briefly a 3 bit flash A/D converter. State the salient issues in designing Flash A/D converters.

- 8.a) Discuss in detail the nois shaped delta sigma modulator.

- b) Write an account of band pass over sampling converters.

#### CMOS DIGITAL INTEGRATED CIRCUIT DESIGN

#### UNIT –I:MOS DESIGN

Pseudo NMOS Logic – Inverter, Inverter threshold voltage, Output high voltage, Output Low voltage, Gain at gate threshold voltage, Transient response, Rise time, Fall time, Pseudo NMOS logic gates, Transistor equivalency, CMOS Inverter logic.

#### **UNIT –II: Combinational MOS Logic Circuits:**

MOS logic circuits with NMOS loads, Primitive CMOS logic gates – NOR & NAND gate, Complex Logic circuits design –Realizing Boolean expressions using NMOS gates and CMOS gates, AOI and OIA gates, CMOS full adder, CMOS transmission gates, Designing with Transmission gates.

#### **UNIT –III: Sequential MOS Logic Circuits:**

Behavior of bistable elements, SR Latch, Clocked latch and flip flop circuits, CMOS D latch and edgetriggered flipflop.

#### **UNIT –IV: Dynamic Logic Circuits:**

Basic principle, Voltage Bootstrapping, Synchronous dynamic pass transistor circuits, Dynamic CMOS transmission gate logic, High performance Dynamic CMOS circuits.

UNIT -: Semiconductor Memories:

Types, RAM array organization, DRAM – Types, Operation, Leakage currents in DRAM cell and refresh operation, SRAM operation Leakage currents in SRAM cells, Flash Memory-NOR flash and NAND flash.

#### **TEXT BOOKS:**

- 1. Digital Integrated Circuit Design –Ken Martin, Oxford University Press, 2011.

- 2. CMOS Digital Integrated Circuits Analysis and Design Sung-Mo Kang, Yusuf Leblebici, TMH, 3<sup>rd</sup> Ed., 2011.

#### **REFERENCE BOOKS:**

- 1. Introduction to VLSI Systems: A Logic, Circuit and System Perspective Ming-BO Lin, CRC Press, 2011

- 2. Digital Integrated Circuits –A Design Perspective, Jan M. Rabaey, Anantha Chandrakasan, Borivoje Nikolic, 2<sup>nd</sup> Ed., PHI.

#### **COURSE COVERAGE SUMMARY**

#### **CMOS DIGITAL IC DESIGN**

| S.No | TEXT BOOK<br>TITLE                      | Chapters<br>in Text<br>Book | Units / Topics Covered                                | AUTHOR                      | PUBLISHERS                     | EDITI<br>ON     |

|------|-----------------------------------------|-----------------------------|-------------------------------------------------------|-----------------------------|--------------------------------|-----------------|

| 1    |                                         | 1,2                         | UNIT-I<br>MOS<br>Design                               |                             |                                |                 |

|      | Digital Integrated<br>Circuit Design    | 2,3                         | UNIT-II<br>Combinatio<br>nal MOS<br>logic<br>circuits | Ken Martin                  | Oxford<br>Universit<br>y press | 2011            |

|      |                                         | 4,5                         | UNIT-III<br>Sequential<br>MOS logic<br>Circuits       |                             |                                |                 |

| 2    | CMOS Digital                            | 2,3                         | UNIT-IV<br>Dynamic<br>logic<br>circuits               | Sung-Mo                     |                                | 3 <sup>rd</sup> |

|      | integrated circuits analysis and design | 4,5                         | UNIT-V<br>Semicondu<br>ctor<br>memories               | Kang,<br>Yusuf<br>Leblebici | ТМН                            | .,2011          |

#### M. Tech – I Semester Regular/Supplementary Examinations, April, 2015 CMOS DIGITAL IC DESIGN

Time: 3 Hours

Max Marks: 60

Answer any FIVE questions

All questions carry EQUAL marks

\*\*\*\*

- 1(a) What are the criteria for voltage threshold for high level and low level in NMOS inverter characteristics? Explain.

- (b) Determine the pull-up to pull-down ratio for an NMOS inverter.

- 2.(a) Explain the voltage transfer characteristics of a CMOS inverter with a neat diagram.

- (b) How the MOS inverters connected in cascade can drive large capacitive loads? Explain.

- 3.(a) Draw the CMOS full adder circuit and explain it s operation.

- (b) Explain the propagation delay and power consumption issues of CMOS gate.

- 4.(a) Draw the logic diagram of a CMOS clocked SR flip-flop and explain with the help of a truth table.

- (b) Differentiate static and dynamic latches.

- 5(a) Explain the speed and power dissipation in dynamic CMOS logic.

- (b) What are the various issues in CMOS dynamic logic design? Explain anyone with a neat sketch.

- 6.(a) What are the types of DRAM? Explain any one.

- (b) Describe the leakage currents in DRAM cell.

- 7.(a) Explain the principle of NOR gate flash memory with a neat diagram.

- (b) Compare the SRAM and DRAM.

- 8. Write short notes on

- (a) Pseudo NMOS logic gate

- (b) Dynamic pass transistor

### **II-SEMESTER**

#### EMBEDDED REAL TIME OPERATING SYSTEMS

#### UNIT - I:

#### Introduction

Introduction to UNIX/LINUX, Overview of Commands, File I/O,( open, create, close, lseek, read,write), Process Control ( fork, vfork, exit, wait, waitpid, exec.

#### **UNIT - II:**

#### **Real Time Operating Systems**

Brief History of OS, Defining RTOS, The Scheduler, Objects, Services, Characteristics of RTOS, Defining a Task asks States and Scheduling, Task Operations, Structure, Synchronization,

#### Communication and Concurrency.

Defining Semaphores, Operations and Use, Defining Message Queue, States, Content, Storage, Operations and Use

#### **UNIT - III:**

#### Objects, Services and I/O

Pipes, Event Registers, Signals, Other Building Blocks, Component Configuration, Basic I/O Concepts, I/O Subsystem

#### **UNIT - IV:**

#### **Exceptions, Interrupts and Timers**

Exceptions, Interrupts, Applications, Processing of Exceptions and Spurious Interrupts, Real Time Clocks, Programmable Timers, Timer Interrupt Service Routines (ISR), Soft Timers, Operations.

#### UNIT - V:

#### **Case Studies of RTOS**

RT Linux, MicroC/OS-II, Vx Works, Embedded Linux, Tiny OS, and Basic Concepts of Android OS.

#### **TEXT BOOKS:**

1. Real Time Concepts for Embedded Systems – Qing Li, Elsevier, 2011

#### **REFERENCE BOOKS:**

- 1. Embedded Systems- Architecture, Programming and Design by Rajkamal, 2007, TMH.

- 2. Advanced UNIX Programming, Richard Stevens

- 3. Embedded Linux: Hardware, Software and Interfacing Dr. Craig Hollabaugh

# EMBEDDED REAL TIME OPERATING SYSTEMS COURSE COVERAGE SUMMARY

|      | TEXT BOOK | T                        | 1                            |                | Ι       |

|------|-----------|--------------------------|------------------------------|----------------|---------|

| S.No | TITLE     | Chapters in<br>Text Book | Units /<br>Topics<br>Covered | PUBLISHER<br>S | EDITION |

| 1    |           |                          |                              |                |         |

|      | EMBEDDED  |                          |                              |                |         |

|      | REAL TIME | 1.ADVANCE                | I                            | RICHARD        |         |

|      | OPERATING | D UNIX                   |                              | STEVENS        |         |

|      |           | PROGRAMMI                |                              |                |         |

|      | SYSTEM    | NG                       |                              |                |         |

|      |           |                          |                              |                |         |

|      |           | 2.REAL TIME              | II,IV                        | JANE           | PHI     |

|      |           |                          |                              |                |         |

|      |           | SYSTEMS                  |                              | W.S.LIU        |         |

|      | EMBEDDED  | 3.REAL TIME              | Ш                            | C.M.KRIS       | ТМН     |

|      | REAL TIME | SYSTEMS                  |                              | HNA,           |         |

| 2    | OPERATING |                          |                              | KANG<br>G.SHIN |         |

|      | SYSTEM    | 4.VX WORKS               |                              |                |         |

|      |           | PROGRAMM ERS             | V                            |                |         |

|      |           | GUIDE                    |                              |                |         |

|      |           |                          |                              |                |         |

|      |           |                          |                              |                |         |

|      |           |                          |                              |                |         |

|      |           |                          |                              |                |         |

|      |           |                          |                              |                |         |

#### Code No: D0604, D5703, D7703, D6803

### JAWAHARLAL NEHRU TECHNOLOGICAL UNIVERSITY HYDERABAD

M.Tech II- Semester Regular Examinations September, 2010 EMBEDDED REAL TIME OPERATING SYSTEMS

(COMMON TO DIGITAL SYSTEMS & COMPUTER ELECTRONICS, VLSI SYSTEMS DESIGN/ VLSI/ VLSI DESIGN, EMBEDDED SYSTEMS & VLSI DESIGN, VLSI & EMBEDDED SYSTEMS)

Time: 3hours Max. Marks: 60 Answer any five questions

| -              | inc. Should mak marks. of miswer any five questions                                                                                        |               |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------|---------------|

|                | All questions carry equal marks                                                                                                            |               |

| 6. a) \        | Write an algorithm for fork.  How many types of system calls are there for messages? Write the algorithm for  Msgsnd.                      | [12]          |

| *              | What is a signal in UNIX? Explain classification of different groups of sig Explain the necessary algorithm for attaching a shared memory. | nals.<br>[12] |

| ,              | Differentiate between hard and soft real time systems.  Discuss about the temporal parameters of real time workload.                       | [12]          |

| 4. a)<br>b)    | Explain the necessity of RTOS in an embedded system.  Explain the weighted round robin and priority driven approaches of reatime           | l             |

|                | scheduling.                                                                                                                                | [12]          |

| 5. a) What are | e the steps that almost eliminate a likely bug in program due to shared data problem?                                                      | ì             |

| b) I           | Discuss about priority Inversion problem and deadlock situation.                                                                           | [12]          |

| 6.             | What are the goals of operating system services? Discuss process management in                                                             | S             |

|                | detail.                                                                                                                                    | [12]          |

|                | Discuss different ways of responding to a hardware resource call on interr What are the salient features of $\mu cos$ ?                    | upts. [12]    |

|                | What are the important functions present in kernelLib.h of Vxworks. Create a mutex semaphore using Vx works.                               | [12]          |

\*\*\*\*

#### Code No: A3805

# JAWAHARLAL NEHRU TECHNOLOGICAL UNIVERSITY HYDERABAD M.Tech I Semester Regular Examinations March/April 2010 EMBEDDED & REAL TIME SYSTEMS

#### (DIGITAL ELECTRONICS & COMMUNICATION SYSTEMS)

Time: 3hours Max.Marks:60

#### Answer any five questions All questions carry equal marks

- - -

- 1. Discuss about any four synthesis design Technologies.

- 2.a) What is meant by Hardware/Software co-simulation. Explain?

- b) Discuss about Priority inversion problem?

- c) Give the main features of Embedded Linux?

- 3.a) What are message queues? How to implement them?

- b) Explain the concept and implementation mechanism of pipes and signals?

- 4.a) Explain Scheduling algorithms of Embedded Task Scheduler?

- b) Discuss about semaphores and mutex?

- 5.a) What are concurrent processes? Explain how embedded software should deal concurrent processes?

- b) How to deal synchronization problems among processes? Explain with specific algorithms?

- 6.a) Discuss about Digital Signal Processor?

- b) Discuss basic features and frame format of Ethernet?

- 7. Write short notes on the following:

- i) RT-level Combinational logic.

- ii) Optimization of custom single purpose processors.

- iii) Goals of Embedded system.

- 8. Write short notes on:

- i) Features of Real time OS.

- ii) Blue tooth.

- iii) PSM-model.

---000---